|

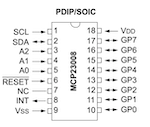

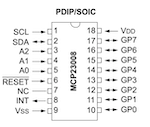

PU2CLR MCP23008 Arduino Library

1.0.7

Arduino Library for MCP23008 Device - By Ricardo Lima Caratti

|

|

PU2CLR MCP23008 Arduino Library

1.0.7

Arduino Library for MCP23008 Device - By Ricardo Lima Caratti

|

#include <Arduino.h>#include <Wire.h>Go to the source code of this file.

Data Structures | |

| union | mcp23008_ioncon |

| IOCON register structure - I/O EXPANDER CONFIGURATION REGISTER (ADDR 0x05) More... | |

| class | MCP |

| struct | mcp23008_ioncon.arg |

Macros | |

| #define | REG_IODIR 0x00 |

| Controls the direction of the data I/O. When a bit is set, the corresponding pin becomes an input. When a bit is clear, the corresponding pin becomes an output. More... | |

| #define | REG_IPOL 0x01 |

| The IPOL register allows the user to configure the polarity on the corresponding GPIO port bits. More... | |

| #define | REG_GPINTEN 0x02 |

| The GPINTEN register controls the interrupt-on-change feature for each pin. More... | |

| #define | REG_DEFVAL 0x03 |

| The default comparison value is configured in the DEFVAL register. More... | |

| #define | REG_INTCON 0x04 |

| The INTCON register controls how the associated pin value is compared for the interrupt-on-change feature. More... | |

| #define | REG_IOCON 0x05 |

| The IOCON register contains several bits for configuring the device. See method: setIoCon. More... | |

| #define | REG_GPPU 0x06 |

| The GPPU register controls the pull-up resistors for the port pins. More... | |

| #define | REG_INTF 0x07 |

| The INTF register reflects the interrupt condition on the port pins of any pin that is enabled for interrupts via the GPINTEN register. More... | |

| #define | REG_INTCAP 0x08 |

| The INTCAP register captures the GPIO port value at the time the interrupt occurred. More... | |

| #define | REG_GPIO 0x09 |

| The GPIO register reflects the value on the port. More... | |

| #define | REG_OLAT 0x0A |

| The OLAT register provides access to the output latches. More... | |

| #define | GPIO_INPUT 0xFF |

| #define | GPIO_OUTPUT 0x00 |

| #define | INTERRUPT_ODR_OPEN_DRAIN 1 |

| Open-drain output (overrides the INTPOL bit). More... | |

| #define | INTERRUPT_ODR_ACTIVE_DRIVE 0 |

| Active driver output (INTPOL bit sets the polarity). More... | |

| #define | INTERRUPT_INTPOL_ACTIVE_HIGH 1 |

| Active high - polarity of the INT output pin. More... | |

| #define | INTERRUPT_INTPOL_ACTIVE_LOW 0 |

| Active low - polarity of the INT output pin. More... | |

| #define | MCP_GPIO0 0 |

| #define | MCP_GPIO1 1 |

| #define | MCP_GPIO2 2 |

| #define | MCP_GPIO3 3 |

| #define | MCP_GPIO4 4 |

| #define | MCP_GPIO5 5 |

| #define | MCP_GPIO6 6 |

| #define | MCP_GPIO7 7 |

| #define | CHECK_BIT_HIGH(x, y) ( x & (1 << y) ) |

| Check if a bit is high. Returns 0 or != 0. More... | |

| union mcp23008_ioncon |

IOCON register structure - I/O EXPANDER CONFIGURATION REGISTER (ADDR 0x05)

The IOCON register contains several bits for configuring the device.

| Data Fields | ||

|---|---|---|

| struct mcp23008_ioncon | arg | |

| uint8_t | raw | |

| struct mcp23008_ioncon.arg |

| #define REG_IODIR 0x00 |

Controls the direction of the data I/O. When a bit is set, the corresponding pin becomes an input. When a bit is clear, the corresponding pin becomes an output.

| #define REG_IPOL 0x01 |

The IPOL register allows the user to configure the polarity on the corresponding GPIO port bits.

| #define REG_GPINTEN 0x02 |

The GPINTEN register controls the interrupt-on-change feature for each pin.

| #define REG_DEFVAL 0x03 |

The default comparison value is configured in the DEFVAL register.

| #define REG_INTCON 0x04 |

The INTCON register controls how the associated pin value is compared for the interrupt-on-change feature.

| #define REG_IOCON 0x05 |

The IOCON register contains several bits for configuring the device. See method: setIoCon.

| #define REG_GPPU 0x06 |

The GPPU register controls the pull-up resistors for the port pins.

| #define REG_INTF 0x07 |

The INTF register reflects the interrupt condition on the port pins of any pin that is enabled for interrupts via the GPINTEN register.

| #define REG_INTCAP 0x08 |

The INTCAP register captures the GPIO port value at the time the interrupt occurred.

| #define REG_GPIO 0x09 |

The GPIO register reflects the value on the port.

| #define REG_OLAT 0x0A |

The OLAT register provides access to the output latches.

| #define GPIO_INPUT 0xFF |

| #define GPIO_OUTPUT 0x00 |

| #define INTERRUPT_ODR_OPEN_DRAIN 1 |

Open-drain output (overrides the INTPOL bit).

| #define INTERRUPT_ODR_ACTIVE_DRIVE 0 |

Active driver output (INTPOL bit sets the polarity).

| #define INTERRUPT_INTPOL_ACTIVE_HIGH 1 |

Active high - polarity of the INT output pin.

| #define INTERRUPT_INTPOL_ACTIVE_LOW 0 |

Active low - polarity of the INT output pin.

| #define MCP_GPIO0 0 |

| #define MCP_GPIO1 1 |

| #define MCP_GPIO2 2 |

| #define MCP_GPIO3 3 |

| #define MCP_GPIO4 4 |

| #define MCP_GPIO5 5 |

| #define MCP_GPIO6 6 |

| #define MCP_GPIO7 7 |

| #define CHECK_BIT_HIGH | ( | x, | |

| y | |||

| ) | ( x & (1 << y) ) |

Check if a bit is high. Returns 0 or != 0.